еҺҹжқҘиҠҜзүҮдёҠзҡ„з”өи·ҜдёҚеҸӘжҳҜе№ійқўзҡ„,иҖҢжҳҜдёүз»ҙз«ӢдҪ“зҡ„( дәҢ )

з‘һеЈ«е…үжәҗзҡ„йёҹзһ°еӣҫдёҚиҝҮ пјҢ жң¬ж¬Ўз ”究зҡ„иҙҹиҙЈдәә пјҢ еҗҢж—¶д№ҹжҳҜиҜҘи®әж–Үзҡ„第дёҖдҪңиҖ…иҺ«е°”е…ӢВ·йңҚеӢ’пјҲMirko HollerпјүиғёжңүжҲҗз«№зҡ„еңЁж–Үз« дёӯиЎЁзӨәпјҡйҖҡиҝҮдҪҝз”ЁжӣҙеӨҡзҡ„и®Ўз®—жңәгҖҒж”№иҝӣе®һйӘҢиЈ…зҪ®д»ҘеҸҠXе°„зәҝжәҗ пјҢ дјҡе°ҶиҝҷдёҖе®һйӘҢжүҖйңҖзҡ„ж—¶й—ҙзј©зҹӯиҮізҺ°еңЁзҡ„еҚғеҲҶд№ӢдёҖ гҖӮйҷӨжӯӨд№ӢеӨ– пјҢ жӣҙе…·жҢ‘жҲҳжҖ§зҡ„зҡ„дёҖзӮ№еңЁдәҺпјҡй—»еҗҚзҡ„вҖңж‘©е°”е®ҡеҫӢвҖқй©ұдҪҝзқҖиҠҜзүҮеҲ¶йҖ е•Ҷ们иҝһе№ҙжҺЁеҮәе°әеҜёжӣҙе°Ҹзҡ„жҷ¶дҪ“з®Ў гҖӮ еңЁиҝҷз§Қжғ…еҶөдёӢ пјҢ дәә们и§ӮеҜҹиҠҜзүҮжүҖз”Ёзҡ„вҖңж”ҫеӨ§й•ңвҖқд№ҹйңҖиҰҒжӢҘжңүиҮӘе·ұзҡ„вҖңж‘©е°”е®ҡеҫӢвҖқ пјҢ жүҚдёҚиҮідәҺеңЁиҝҷеңәз«һиөӣдёӯиҗҪдёӢеӨӘиҝң гҖӮе°ұзҺ°еңЁзҡ„жғ…еҪўжқҘзңӢ пјҢ иҠҜзүҮеҲ¶йҖ е•Ҷ们已з»ҸеҚ дәҶдёҠйЈҺ гҖӮ еңЁжң¬ж¬Ўз ”究дёӯ пјҢ иҺ«е°”е…ӢВ·йңҚеӢ’жүҖе®һзҺ°зҡ„жңҖй«ҳеҲҶиҫЁзҺҮзәҰдёә 14.6 зәізұі пјҢ е°Ҫз®ЎиҝҷдёҖж•°еӯ—еҚҒеҲҶдәҶдёҚиө· пјҢ еҸҜзӣ®еүҚз”ұиӢұзү№е°”ејҖеҸ‘зҡ„жңҖж–°дёҖд»Јзҡ„еӨ„зҗҶеҷЁиҠҜзүҮ пјҢ еҚҙе·Із»ҸиҝҲиҝӣдәҶ10зәізұіеҲ¶зЁӢзҡ„й—Ёж§ӣ гҖӮж— и®әжҖҺд№ҲиҜҙ пјҢ иҝҷж¬ЎиҺ«е°”е…Ӣзӯүдәәзҡ„з ”з©¶е°ҶеңЁвҖңиҠҜзүҮж— жҚҹжЈҖжөӢвҖқйўҶеҹҹдёҠз•ҷдёӢжө“еўЁйҮҚеҪ©зҡ„дёҖ笔 гҖӮ йҡҸзқҖиҝҷйЎ№жҠҖжңҜзҡ„иҝӣдёҖжӯҘеҸ‘еұ• пјҢ жҲ–и®ёеңЁдёҚиҝңзҡ„е°ҶжқҘ пјҢ иҠҜзүҮеҶ…йғЁз»“жһ„зҡ„жЈҖи§ҶдёҚеҶҚжҳҜвҖңдёҖй”Өеӯҗд№°еҚ–вҖқ гҖӮзӣёеҸҚзҡ„ пјҢ еҪ“дәә们е°ҶиҠҜзүҮж”ҫе…ҘжҹҗдёӘзұ»дјјзҡ„иЈ…зҪ®д№ӢеҗҺ пјҢ еҚіеҸҜдёҖи§ҲиҠҜзүҮзҡ„еҶ…йғЁжһ„йҖ гҖӮ д»ҺиҝҷдёӘж„Ҹд№үдёҠиҜҙ пјҢ иҠҜзүҮзҡ„и®ҫи®Ўдјјд№ҺеҸҳеҫ—вҖңйҖҸжҳҺвҖқдәҶ гҖӮ

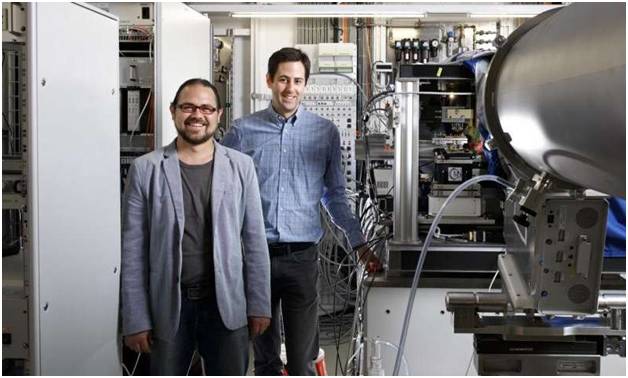

и®әж–Үзҡ„дҪңиҖ…Mirko HollerпјҲеҸіпјүдёҺ Manuel Guizar-SicairosпјҲе·ҰпјүдёҺжӯӨеҗҢж—¶ пјҢ еҜ№дәҺиҠҜзүҮеҲ¶йҖ е•ҶжқҘиҜҙ пјҢ иҝҷдёҖжҠҖжңҜзҡ„й—®дё–ж— з–‘е°ҶдјҡеҜ№иҝҷдёӘиЎҢдёҡдә§з”ҹж·ұиҝңзҡ„еҪұе“Қ гҖӮ йҖҡиҝҮжЈҖи§ҶиҠҜзүҮеҶ…йғЁжҳҜеҗҰеӯҳеңЁеҲ¶йҖ зјәйҷ·иҝҷдёҖеҒҡжі• пјҢ еҲ¶йҖ 们еҸҜд»ҘеҖҹжӯӨе®һиЎҢжӣҙеҠ дёҘж јзҡ„иҙЁйҮҸжҺ§еҲ¶е’Ңе“ҒиҙЁз®ЎзҗҶж–№й’Ҳ гҖӮйҷӨжӯӨд№ӢеӨ– пјҢ дәә们иҝҳиғҪеҲ©з”ЁиҝҷйЎ№жҠҖжңҜжқҘзЎ®и®ӨйӣҶжҲҗз”өи·Ҝи®ҫи®Ў пјҢ дәҶи§Је…¶еҶ…йғЁеҠҹиғҪ пјҢ дјҳеҢ–е…¶з”ҹдә§жөҒзЁӢ пјҢ 并жүҫеҮәеҸҜиғҪзҡ„еӨұж•ҲжңәеҲ¶ гҖӮд»Һж¶Ҳиҙ№иҖ…зҡ„и§’еәҰзңӢ пјҢ иҝҷдёҖжҠҖжңҜеҗҢж ·жғ№дәәе…іжіЁ гҖӮ жңҖиҝ‘ пјҢ 硬件е®үе…Ёд№ҹж—ҘзӣҠжҲҗдёәдәҶдёҖдёӘйўҮеҸ—йҮҚи§Ҷзҡ„иҜқйўҳ гҖӮ зү№еҲ«жҳҜеҜ№дәҺеӣҪйҳІе’ҢеҶӣе·ҘиЎҢдёҡиҖҢиЁҖ пјҢ еҰӮжһңиғҪе°ҶиҝҷйЎ№жҠҖжңҜиғҪеӨҹеҠ д»Ҙиҝҗз”Ё пјҢ 他们дҫҝеҸҜд»ҘзЎ®и®Ө пјҢ иҠҜзүҮеҶ…йғЁжҳҜеҗҰеӯҳеңЁеҸҜиғҪзӘғеҸ–жңәеҜҶзҡ„жҒ¶ж„Ҹ硬件 пјҢ еҚіжүҖи°“зҡ„вҖң硬件жңЁй©¬вҖқ гҖӮ жҜ•з«ҹ пјҢ дёҖеқ—иў«з ёеқҸдәҶзҡ„иҠҜзүҮеҸҜжҳҜжІЎжңүеҚҠзӮ№з”ЁеӨ„зҡ„ гҖӮж—¶иҮід»Ҡж—Ҙ пјҢ иҠҜзүҮж— жҚҹжЈҖжөӢзҡ„еҸ‘еұ•е°ҡжңӘжҲҗзҶҹ пјҢ дҪҶжҳҜз‘һеЈ«дҝқзҪ—и°ўеӢ’з ”з©¶йҷўзҡ„科еӯҰ家们дёәзңҹжӯЈзҡ„вҖңйҖҸжҳҺиҠҜзүҮвҖқзҡ„жңӘжқҘз…§дә®дәҶе…Ёж–°зҡ„и·Ҝеҫ„ гҖӮ

жҺЁиҚҗйҳ…иҜ»

- д»Ҡе№ҙеӨ§дјҷйЎҝжӮҹпјҡеҺҹжқҘж„ҹеҶ’зңҹзҡ„жҳҜеӨҡе–қж°ҙе°ұеҸҜд»ҘеҘҪ

- еҚҠеІӣйғҪеёӮжҠҘ|еЈ®жұүиӢҰз»ғиҗқиҺүйҹіиҜҲйӘ—50дёҮпјҒзҪ‘еҸӢпјҡеҺҹжқҘиҝҷе°ұжҳҜдј иҜҙдёӯзҡ„вҖңејҖеҸЈи·ӘвҖқ

- зҠҜзҪӘ|зҹӯзҹӯеҚҒдҪҷеӨ©пјҢйқ жү“йә»е°ҶиҺ·еҲ©1дёҮдҪҷе…ғпјҢеҺҹжқҘиҝҷдәәжү“йә»е°Ҷжңүеё®жүӢиҝҳвҖңејҖжҢӮвҖқ

- 科жҠҖе°Ҹи®°иҖ…|з©әе§җеңЁйЈһжңәдёҠжҖҺд№Ҳдј‘жҒҜпјҹеҺҹжқҘиҝҳжңүиҝҷдәӣеҜҶе®ӨпјҢзңӢдәҶд№ӢеҗҺжҲ‘зңҹзҡ„еҫҲзҫЎж…•

- йқ’е№ҙ|жҲ‘家ж°ҙиЎЁи¶ҠиҪ¬и¶Ҡеҝ«пјҢж°ҙиҙ№еӨҡдәҶ2еҖҚпјҢеҺҹжқҘдёҚжҳҜжјҸж°ҙй—®йўҳеҮәеңЁиҝҷ

- дёӯе№ҙ|жҡ–еҝғпјҒйғ‘е·һдёҖж— дё»з®Ўе°ҸеҢәи·ҜзҒҜиў«зӮ№дә®пјҢеҺҹжқҘйқ зҡ„жҳҜиҝҷеё®дё“дёҡзҡ„еҝ—ж„ҝиҖ…

- жӯЈиғҪйҮҸ|жңҙе®һй“ёе°ұз№ҒеҚҺпјҢе№іеҮЎд№ӢдёӯеҪ°жҳҫдјҹеӨ§пјҢеҺҹжқҘпјҢе–„иүҜжҳҜеҸҜд»Ҙдә’йҖҡзҡ„

- иҙөйҳізҪ‘|иҙөйҳідёҖз”·еӯҗиў«йӮ»еұ…жҸҗеҲҖиҝҪиө¶пјҢеҺҹжқҘжҳҜиё©еҲ°зӢ—еұҺеҗҺжүҫйӮ»еұ…зҗҶи®әеҸ‘з”ҹдәүеҗө

- йЈһиЎҢзҡ„е°ҸзҢӘ|з”өе·ҘеҹәзЎҖпјҡRLз”өи·Ҝзҡ„е“Қеә”пјҲ43пјү

- дҝЎжҒҜж—¶жҠҘ|еҠһж— зҪӘиҜҒжҳҺпјҢжүҚеҸ‘зҺ°иҮӘе·ұз«ҹжҳҜвҖңжҠўеҠ«зҠҜвҖқпјҹзңҹзӣёеҺҹжқҘжҳҜ...