阿尔法工场研究院|芯之“母”EDA也有中国梦( 二 )

再具体一点:

工程师向EDA提供完整的HDL code(Hardware Description Language , 硬件描述语言代码);

EDA会根据逻辑闸设计图的规格对该代码进行修改和调整 , 生成功能正确的电路图;

最后供给后端进行布局模拟和电路制作 , 形成光罩 , 然后流片成产品

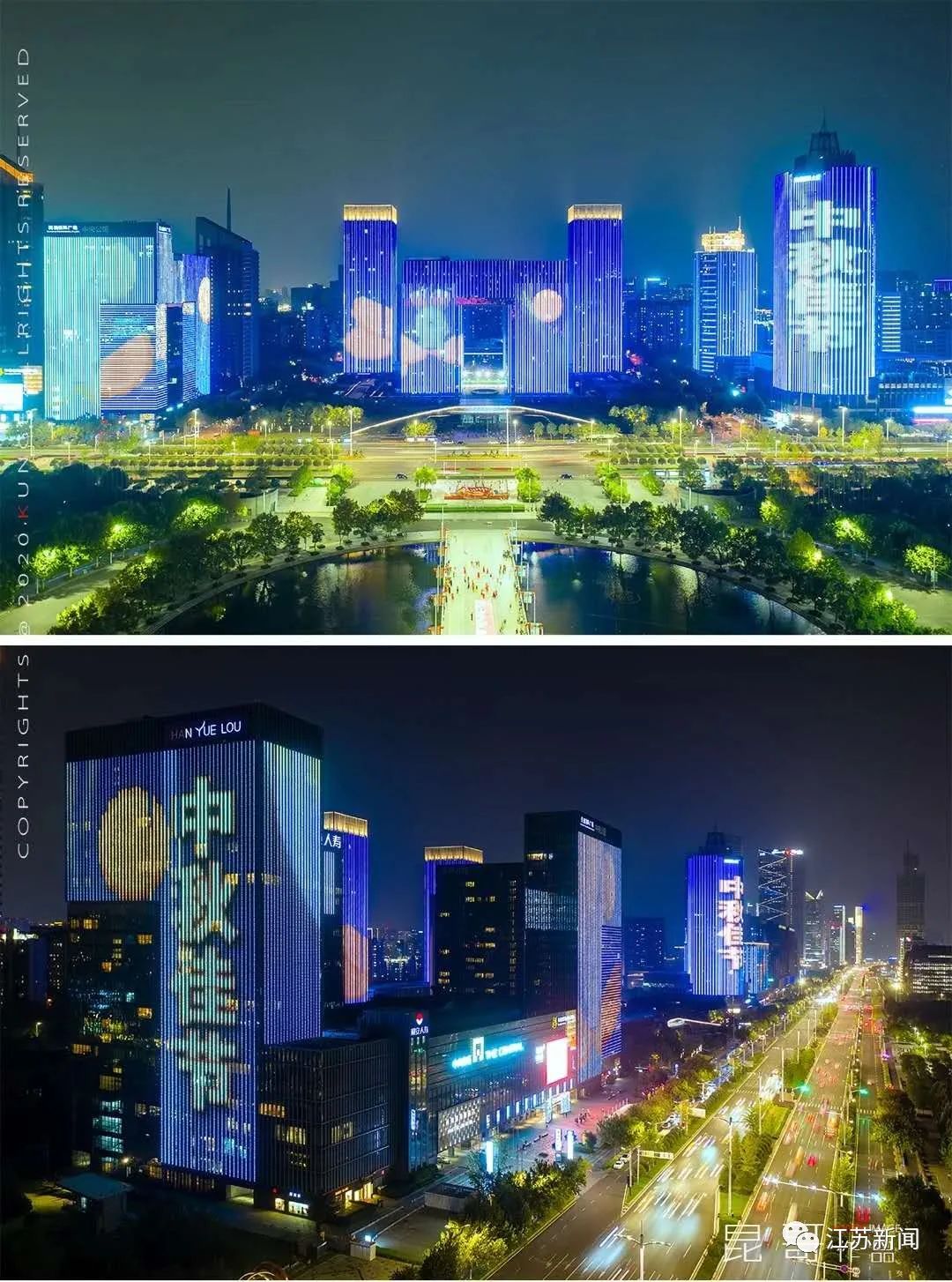

本文插图

(EDA三巨头之一Cadence的产品界面展示)

作为逻辑综合工具的EDA , 不仅为设计的逻辑闸提供意见的修改 , 其更重要的价值是在SoC(System on Chip , 系统级芯片)数以亿计的今天 , 大幅度地降低了设计试错成本 。

大规模集成电路的复杂度 , 已经远超人类设计仿真的控制极限 。 因此 , 在动辄流片费用百万千万计的今天 , 任何一家芯片公司都无法承受数次流片失败的成本 。 设计环节的丝毫差错 , 都可能导致巨大的财务损失 。

EDA的出现 , 至少将此成本缩减超百倍 。

随后 , 集成电路的布道者们开始大肆宣传集成电路与承载的人类命运 , 几乎和集成电路所能承载的复杂程度直接关联 。 这在当时看起来几乎荒诞的理论 , 在40年后的今天一语中的 ——

通过编程语言设计和验证电路预期行为 , 并通过逻辑综合工具软件得到低抽象级物理设计的研发途径 , 迄今为止仍然是数字集成电路设计的思想基础和工程基础 。

在这个基础之上 , EDA的商业化在上世纪80年代高速发展:

1981年 , 日后主宰全球EDA市场的三大巨头之一Mentor Graphics悄然诞生 , 日后名声飞扬的Xpedition、PADS、Mentor EE均诞生于此;

1986年 , Gateway提出Verilog , 这是迄今为止最流行的高级抽象语言;

同年 , 三巨头之二Synopsys诞生于美国加州Mountain View;

1987年 , 美国国防部资助的VHDL(Very-High-Speed Integrated Circuit Hardware Description Language , 超高速集成电路硬件描述语言)问世 , 将设计实体分为内外部分 , 日后被广泛应用于机械工程、仪器科学和计算机科学中;

1988年 , 第三家巨头Cadence诞生在美国加州San Jose 。

产业规模的急速扩张和竞争逐步加剧 , 导致分工模式进一步细化 。

EDA犹如达摩克斯的利剑 , 精确切分原来由IDM (Integrated Device Manufacturer , 集约化制造商)主导的半导体产业生态 , 逐步演化成了Fabless(无工厂仅设计) + Foundry(代工厂) + OSAT(Out Sourced Assembly and Testing , 封测代工厂)的产业格局 。

后来耳熟能详的IC设计、IC制造和IC封装 , 三大核心板块逐渐形成 。

本文插图

(来源:电子产品世界EEPW)

因为EDA , 产业生态的上中下游 , 第一次被清晰的展现出来 。

“当价格不变时 , 集成电路上可容纳的元器件的数目 , 约每隔18-24个月便会增加一倍 , 性能也将提升一倍 。 ”

——戈登·摩尔(英特尔创始人之一)

摩尔定律作为半导体行业的金科玉律已运转多年 , 应验了无数半导体发展的重大时刻 , 并像圣经一般 , 收敛了整个芯片产业上下游的发展和演化规律 , 使其达到了实质意义上的统一 。

而EDA的迭代 , 数年来也追随摩尔定律有序发展 , 承载了人类迄今为止超大规模集成电路的设计 , 发展和产业化演进 。

但凡事终有极限 , 物理性征的限制 , 使得摩尔定律大有被替代更新的趋势 。

在2019年人类撬开7nm大门后 , 传统EDA支撑下的IC设计遭遇瓶颈 , 对复杂设计的不断追求和提升集成电路性能 , 并缩小尺寸的要求进一步提升 。

如何在EDA上追赶并超越摩尔定律 , 成为人类触碰下一代超大规模集成电路的核心要素 —— AI , 物联网和虚拟现实等技术的不断更迭 , 人类对集成电路的要求也越发提升 , 对EDA的智能型要求也愈发提升 。

推荐阅读

- 5G|2020年5G芯片行业研究报告

- 行业互联网|2020年5G芯片行业研究报告

- 互联网|两所高校研究院拟落户!副中心这个国家级产业园最新进展来啦

- 科学|合肥研究院在空间反演对称结构中实现光致纯自旋流

- 每日财报|云从科技或成“AI四小龙”第一股 国家队标签显眼 核心竞争力存疑|IPO研究院

- 工场|金隅智造工场产值将超百亿元

- |让食药材更安全放心,华南协同创新研究院取得一项关键技术突破

- 用友社会化用工研究院|线上营销优势尽显,用友薪福社赋能科技,助企业打通运营闭环

- 赛迪研究院|赛迪研究院成功举办“2020世界半导体大会·高峰论坛、创新峰会”

- 父母|贝壳研究院《95后新社会人婚恋居住调查报告》:过半95后接受情侣租房AA制