硬件|芯片巨头们都在争相研发的3D封装关键技术究竟有多难?( 二 )

Imec正在开发一种使用TCB实现的10μm间距技术,7μm和5μm也正在研发中 。“40μm凸块间距有足够的焊接材料来补偿电流变化 。当缩放到10μm或更小的间距时,情况将会发生变化,” Imec的高级科学家Jaber Derakhshandeh在最近的ECTC会议上的一篇论文中说,“在细间距的微泵中,电流量和良好的连接取决于TCB工具的精度、错位、倾斜以及焊料的变形量 。”

为了延长微型凸块的发展寿命,Imec开发了一种金属垫板工艺,同以前一样,裸片上仍然有微型凸块,不同的是,在Imec工艺中,裸片上还有假金属微凸块,这类凸块类似于支撑架构的小梁 。

Derakhshandeh说:“在3D裸片对晶圆的堆叠中引入了一个假金属微凸块,以减小TCB工具的倾斜误差,并控制焊料变形,从而使粘合裸片不同位置的电阻和成形接头的质量相同 。” 。

混合键合是TCB的补充

在某些时候,微型凸块/支柱和TCB可能会用光,这时候就需要混合键合,它可以用在微凸技术碰壁后或者在此前插入 。

不过微型凸块不会很快在市场上消失,微型凸块和混合键合技术都将在市场上占据一席之地,这取决于具体的应用 。

目前混合键合技术正在发展,台积电最有发言权,其正在研究一种叫做集成芯片系统(SoIC)的技术 。使用混合键合,台积电的SoIC技术可以实现低于微米的键合间距 。据悉,SoIC的缓冲垫间距是现有方案的0.25倍 。高密度版本可以实现10倍以上的芯片到芯片的通信速度,高达近2000倍的带宽密度和20倍的能源效率 。

台积电的SoIC计划于2021年投入生产,可以实现小间距HBM和SRAM存储立方体以及类似3D的芯片架构 。台积电研究员MF Chen在最近的一篇论文中说,与当今HBM相比,“继承了SoIC的DRAM存储器立方体可以提供更高的存储器密度、带宽和功率效率 。”

台积电正在开发芯片对晶圆(Chip-to-Wafer)的混合键合技术 。晶圆键合已经在微机电系统(MEMS)和其他应用中使用多年,且类型众多 。“微电子和微机电系统的制造和封装依赖于两个基板或晶片的键合,” Brewer Science的高级研究化学家Xiao Liu说道,“在微机电系统的制造过程中,器件晶圆将被粘合到另一个晶圆上,以保护敏感的MEMS结构 。直接键合技术(例如熔融键合和阳极键合)或间接键合技术(例如金属共晶、热压键合和胶粘剂键合)都是常用的方法 。使用胶粘剂作为两个基板之间的中间层,处理会更加灵活 。”

铜混合键合最早出现在2016年,当时索尼将这项技术用于CMOS图像传感器,索尼从现在属于Xperi的Ziptronix获得了该技术的许可 。

Xperi的技术称为直接绑定互连(DBI),DBI在传统的晶圆厂中进行,并应用于晶圆对晶圆的键合工艺,在这一过程中,先对晶圆进行处理,然后将金属焊盘凹入表面,使表面变得平滑 。

分离晶圆也经历类似的过程,晶片使用两步工艺键合,首先是电介质互连,然后是金属互连 。

EV Group业务发展总监Thomas Uhrmann表示:“总体而言,晶圆对晶圆是设备制造的首选方法,在整个工艺流程中,晶圆都保留在前端晶圆厂环境中 。在这种情况下,用于混合键合的晶圆制备在界面设计规则、清洁度、材料选择以及激活和对准方面面临诸多挑战 。氧化物表面上的任何颗粒都会产生比颗粒本身大100至1,000倍的空隙 。”

尽管如此,该技术已被证明可用于图像传感器,其他设备正在研究开发中 。Uhrmann说:“计划进一步推出诸如堆叠SRAM到处理器芯片之类的器件 。”

文章图片

混合键合的3D集成,图片源自:Xperi

铜混合键合推动先进封装

对于先进芯片封装,业界还致力于裸片对晶圆和裸片对裸片的铜混合键合,即将裸片堆叠在晶圆上、将裸片堆叠在中介层上或将裸片堆叠在裸片上 。

这比晶圆间键合更加困难 。“对于裸片对晶圆的混合键合而言,处理不带颗粒的裸片的基础设施以及键合裸片的能力成为一项重大挑战 。” Uhrmann说,“虽然可以从晶圆级复制或改写芯片级的界面设计和预处理,但在芯片处理方面仍存在许多挑战 。通常,后端工艺(例如切块、裸片处理和在薄膜框架上的裸片传输)必须适应前端清洁级别,才能在裸片级别获得较高的粘合率 。”

Uhrmann说,“晶圆对晶圆的键合方式正在发展,当我看到这种方式的过程时,看到工具开发的方向时,我认为这是一项非常复杂的集成任务,但是台积电这样的公司正在推动这个行业的发展,我们可以对其抱有期待 。”

封装的混合键合与传统的IC封装在某些方面是不同的 。传统上,IC封装是在一个OSAT(Outsourced Semiconductor Assembly and Test,委外封测代工厂)或封装厂中进行的,而铜混合键合却是在晶圆厂的洁净室中进行,而不是OSAT中 。与传统封装处理尺寸缺陷不同,混合键合对微小的纳米级缺陷非常敏感,需要工厂级的洁净室来防止微小缺陷干扰生产过程 。

缺陷控制至关重要 。赛博光学研发副总裁Tim Skunes说,“考虑到这些工艺使用已知的昂贵优良裸片,失败成本很高 。在组件之间,有一些突起形成垂直的电气连接,控制凸块高度和共面性对于确保堆叠组件之间的可靠性至关重要 。”

推荐阅读

- 马斯克|马斯克推脑机接口芯片:安装不到1小时,植入活猪现场遛

- 硬件|正面刚Apple Watch和Fitbit 亚马逊推出智能手环Halo

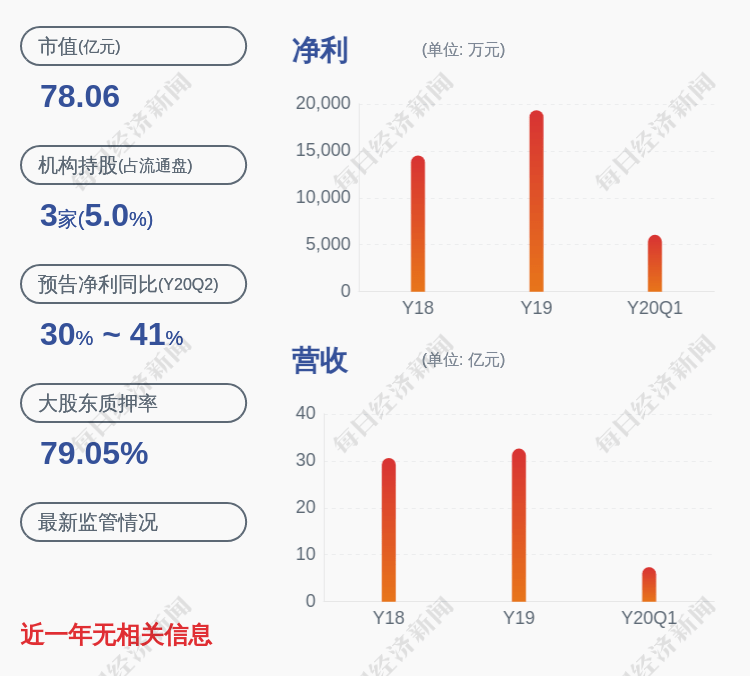

- 从月亏7亿元,到盈利5.5亿元!这家钢铁巨头“涅槃重生”了!

- 张帆|汇顶科技董事长张帆:上半年超薄屏下光学指纹发货超千万,ECG、PPG芯片已量产

- 新浪财经:华为余承东:正在想办法应对美芯片封杀新浪财经2020-08-29 12:03:400阅

- 马斯克|马斯克展示脑机接口:硬币大小芯片植入猪脑,实时读取猪脑信息

- 硬件|Axon推出无证也能在市区飞行的系绳式Fotokite无人机

- 突发|突发!美国又有巨头大裁员,18000人…

- 【】马斯克活猪脑机接口试验成功:多芯片植入、硬币大小、实时读取脑电波 已获批人脑实验2020-08-29 09:56:140阅

- 硬件|FCC曝光Bose或推出配备了扬声器的新款Frames智能太阳镜

![[]银行员工:存款达到“这个数”,每月利息相当于很多人2个月工资](http://img88.010lm.com/img.php?https://image.uc.cn/s/wemedia/s/upload/2020/853d39c4ad136e01fcfb3249ceeb873d.jpg)

![[熊孩子乐园]从来不做这三件事,人缘越来越好,人际交往规则:情商高的人](https://imgcdn.toutiaoyule.com/20200330/20200330145713047207a_t.jpeg)